邹平县建设局网站在线工具

最近一个多月没有写博客了,然后最近工作中也遇到一个复位信号的问题。问题是这样的,关于外部复位信号,之前我们的处理方式都是通过PLL产生的Lock信号作为内部的复位信号。但是由于换到A54上面没有IP核,所以只有不用PLL,改成直接用外部复位信号,这时候问题就来了,发现有些模块并没有上电复位。然后通过异步复位,同步释放的方式解决了该问题。所以再记录学习一下!

1 同步复位

同步复位指的是当时钟上升沿检测到复位信号,执行复位操作。有效的时钟沿是前提

verilog是这样写的

always @(posedge clk) beginif(rst_n)y <= 1'b0;elsey <= b;

end

同步复位的优点有如下:

- 可以使所设计的系统成为100%的同步时序电路,有利于时序分析,而且综合出较高的Fmax

- 由于只有时钟有效电平到来时才有效,所以可以滤除高于时钟频率的复位毛刺

- 有利于仿真器仿真

缺点如下:

- 复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务,同时还要考虑诸如时钟偏移、组合逻辑路径延时、复位延时等因素(所以复位信号有时需要脉冲展宽,用以保证时钟有效期间有足够的复位宽度)

- 由于大多数的逻辑期间的目标库内的DFF都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会一方面额外增加FPGA内部逻辑资源,另一方面也增加了相应的组合逻辑门延时。

2 异步复位

异步复位指的是无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。当时钟上升沿检测到复位信号,执行复位操作。

verilog是这样写的:

always @(posedge clk or negedge rst_n) beginif(rst_n)y <= 1'b0;elsey <= b;

end

异步复位的优点:

- 大多数目标器件库的DFF都有异步复位端口,那么该触发器的复位端口就不需要额外的组合逻辑,这样就可以节省资源

- 设计相对简单

- 异步复位信号产生和相应都很方便(电路在任何情况下都能复位而不管是否有时钟出现)

异步复位的缺点:

- 最大的问题在于它属于异步逻辑,问题出现在复位释放的时候,而不是有效时,如果复位释放接近时钟有效沿,则触发器的输出可能进入亚稳态(此时clk检测到的rstn的状态就会是一个亚稳态,即是0是1是不确定的,从而导致复位失败)

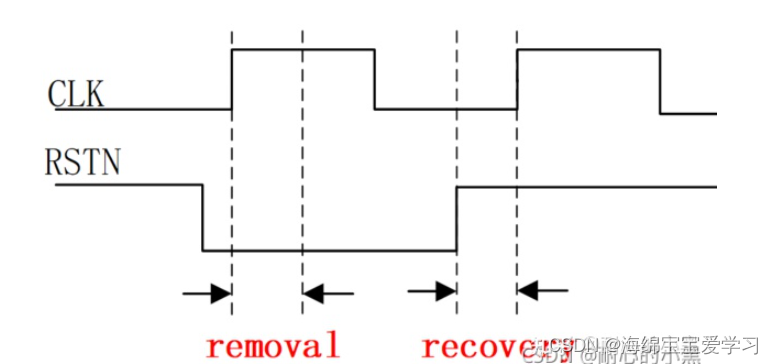

异步复位信号需要满足 recovery time(恢复时间)和 removal time(去除时间),才能有效的复位和释放复位,防止出现亚稳态。

释放复位时,复位信号在时钟有效沿来临之前就需要提前一段时间恢复到非复位状态,这段时间为 recovery time。类似于同步时钟下触发器的 setup time。

复位时,复位信号在时钟有效沿来临之后,还需要在一段时间内保持不变,这段时间为 removal time。类似于同步时钟下触发器的 hold time。

recovery 与 removal time 示意图如下所示。

- 可能因为噪声或者毛刺照成虚假复位信号(比如系统正常工作时突然复位)(注意:时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要注意的问题)

- 总结下来,我们推荐使用异步复位、同步释放的方式,并且复位信号为低电平有效!

进一步解释一下,

1 复位信号到来的有效与否与clk无关,而且复位信号的撤除也与clk无关,但是复位信号的撤除是在下一个clk来到后才起的作用。

2 异步复位同步释放的目的就是为了防止复位信号撤除时,可能产生的亚稳态

异步复位同步释放的代码如下:

always @(posedge clk or negedge rst_async_n) beginif(!rst_async_n) beginrst_s1 <= 1'b0;rst_s2 <= 1'b0;endelse beginrst_s1 <= 1'b1;rst_s2 <= rst_s1;endendassign rst_sync_n = rst_s2;

为什么是 rst_s1 <= 1’b1,因为本身复位时高扇出信号,这样可以减少复位信号的扇出数,1’b1 意思是直接接电源,节省资源,这样可以使电路性能更好

3 继续深入理解复位,同步复位,异步复位,异步复位同步释放

3.1 前言

电路中任何一个寄存器、存储器结构和其他时序单元都必须附加复位逻辑电路,以保证电路能够从错误状态中恢复、可靠性工作。对于综合实现的真实电路,通过复位使电路进入初始状态或者其他预知状态。复位在数字IC设计中是不可缺少的一部分。

3.2 异步复位

一般来说,复位信号有效后会保持比较长的一段时间,确保register被复位完成。但是复位信号释放时,因为其和时钟是异步的关系,我们不知道它会在什么时刻被释放。