西部数码做的网站打不开seo教程之关键词是什么

USB2.0/USB3.0 电路

RK3588 芯片内置两个USB3.0 OTG控制器(内嵌2个USB2.0 OTG,下图绿色处),1个USB3.0 HOST 控制器,2个USB2.0 HOST控制器。 这些控制器与PHY的内部复用图如下:

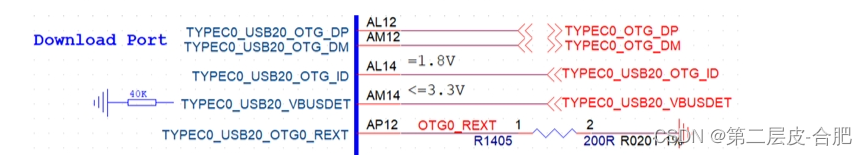

USB3.0 OTG0 控制器支持SS/HS/FS/LS, 内嵌的USB2.0(HS/FS/LS)信号采用USB2.0 OTG PHY, 信号名见下图的红色方框内;RK3588目前仅此接口支持做Fireware的Download,应用中请务必要预留出

USB 3.0 的 SS信号(5Gbps)与 DP1.4复用,采用USB/DP的Combo PHY;信号如下图的红色方框内。

由于USB3.0的OTG和USB2.0的OTG是同一个USB3.0的控制器,因此USB3.0和USB2.0的OTG 只能同时做Device或者做HOST,不能USB3.0的OTG做HOST,USB2.0的OTG做Device或者USB3.0 的OTG做Device而USB2.0的OTG做HOST。 USB3.0 Controller0 和 DP1.4 Controller0 通过USB3.0/DP1.4的Combo PHY0组合成一个完整的TYPEC 口,此Combo PHY支持Display Alter mode,Lane0 和 Lane2 在 DP mode 下做TX,在 USB mode下做RX;

TX和RX共享Lane0和Lane2。 USB3.0 Controller1 和 DP1.4 Controller1 组成的 TYPEC1 口同 TYPEC0 口一样,不再做重复描述。 这个USB3.0/DP1.4 的 Combo PHY 支持Lane间的交换(SWAP),因此一个TYPEC标准口可以有如 下五种的配置:

配置一:Type-C 4Lane(with DP function)

配置二:USB2.0 OTG+DP 4Lane(Swap OFF)

配置三:USB2.0 OTG+DP 4Lane(Swap ON)

配置四:USB3.0 OTG0+DP 2Lane(Swap OFF)

配置五:USB3.0 OTG+DP 2Lane(Swap ON)

USB2.0/USB3.0 设计中请注意:

TYPEC0_USB20_OTG_DP/TYPEC0_USB20_OTG_DM 是系统固件烧写口,如果产品不用这个接 口,在调试与生产过程中必须要预留此接口,不然会无法调试及生产烧写固件;

TYPEC_USB20_OTG0_ID内部有大概200Kohm电阻上拉到USB20_AVDD_1V8;

TYPEC_USB20_VBUSDET是OTG和Device模式检测脚,高有效,2.7-3.3V,TYP:3.0V,建议 在管脚放置一个100nF电容。

OTG模式可以设置以下三种模式:

OTG模式:根据ID脚状态自动切换是device模式或HOST模式,ID高为device,ID拉低为HOST, 处在device 模式时,还会判断VBUSDET脚是否为高(大于2.3V),如果为高,才会拉高DP, 开始枚举;

Device 模式:设置为这个模式时,无需ID脚,只需判断VBUSDET脚是否为高(大于2.3V), 如果为高,才会拉高DP,开始枚举;

HOST模式:设置为这个模式时,ID和VBUSDET状态都无需要关心。(如果产品只需要HOST 模式,但是由于仅TYPEC0_USB20_OTG_DP/ TYPEC0_USB20_OTG_DM是系统固件烧写口,在 调试与生产过程都需要用这个口,烧写和 adb 调试时,需要设置成 device 模式,因此 TYPEC_USB20/1_VBUSDET 信号也必须接)。

TYPEC 协议要求在SSTXP/N线上增加100nF交流耦合电容,AC耦合电容建议使用0201封装,更低 的ESR和ESL,也可减少线路上的阻抗变化。 TYPEC 座子所有信号都必须增加ESD器件,布局时靠近USB连接器放置。对于SSTXP/N,SSRXP/N 信号,ESD寄生电容不得超过0.3pF。

SATA3.0 电路

RK3588 芯片拥有3个SATA3.0控制器,和PCIe以及USB3_HOST2控制器复用PIPE PHY0/1/2,具体路 径请见下图。

支持SATA PM功能,每个port可以支持5个设备;

支持SATA 1.5Gb/s,SATA 3.0Gb/s,SATA 6.0Gb/s speeds ;

支持eSATA。

SATA设计中请注意:

Slot设计时,外围电路及电源需要满足Spec要求;

PCIE20_SATA30_0/1_AVDD_0V85/PCIE20_SATA30_USB30_2_AVDD_0V85 这三路 0.85V 合并 供电,需放置1x10uF+1x1uF +1x100nF去耦电容, 布局时,靠近RK3588管脚放置。 PCIE20_SATA30_0/1_AVDD_1V8/PCIE20_SATA30_USB30_2_AVDD_1V8 三路 1.8V 合并供电, 需放置2x1uF +1x100nF去耦电容,布局时,靠近RK3588管脚放置。

SATA接口的TXP/N,RXP/N 差分信号上串接的10nF交流耦合电容,AC耦合电容建议使用0201 封装,更低的ESR和ESL,也可减少线路上的阻抗变化;

eSATA接口座子所有信号都必须增加ESD器件,布局时靠近座子放置,ESD寄生电容不得超过0.4pF

PCIe2.0

Slot设计时,外围电路及电源需要满足Spec要求;

PCIe2.0接口的TXP/N差分信号上串接的100nF交流耦合电容,AC耦合电容建议使用0201封装, 更低的ESR和ESL,也可减少线路上的阻抗变化;

PCIE2.0_CLKREQn和PCIE20_WAKEn必须使用功能脚,不能用GPIO替代,特别说明:选择时, 必须都是选择_M0或_M1或_M2,不能一个_M0一个_M1;

PCIE20_PERSTn 可以选择功能脚也可以使用 GPIO 替代,选择功能脚时,必须和 PCIE20_CLKREQn 和PCIE20_WAKEn同一组_Mx;

标准的PCIe Slot:PCIE20_CLKREQn,PCIE20_WAKEn,PCIE20_PERSTn为3.3V 电平;

PCIE20_PRSNT为Add In Card插入检测脚,可以使用GPIO;

使用PCIE20功能时候,复用的SATA/USB30功能无法使用,SATA/USB30对应的功能模块说明;

PCIe2.0 功能模块没有使用,数据线 PCIE20_TXP/TXN、PCIE20_RXP/RXN 和参考时钟线 PCIE20_REFCLKP/ REFCLKN 悬空即可;

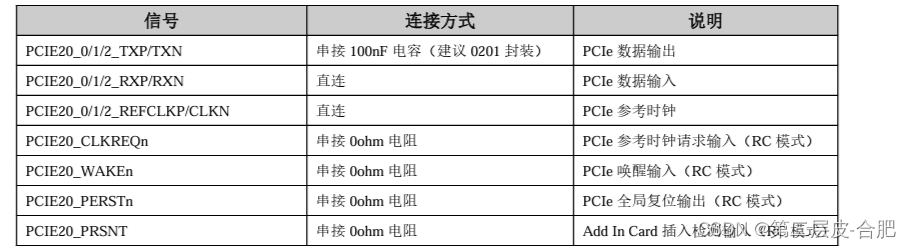

PCIe2.0接口匹配设计推荐如下表所示:

PCIE30_REF_CLKP/N 仅支持输入:

需要提供HCSL电平时钟输入;

必须提供满足PCIe3.0以上的时钟要求;

RK3588 PCIe3.0 X4Lane RC 模式。兼容PCIe3.0 X2Lane RC 模式,

兼容PCIe3.0 X1Lane RC 模式。